Content

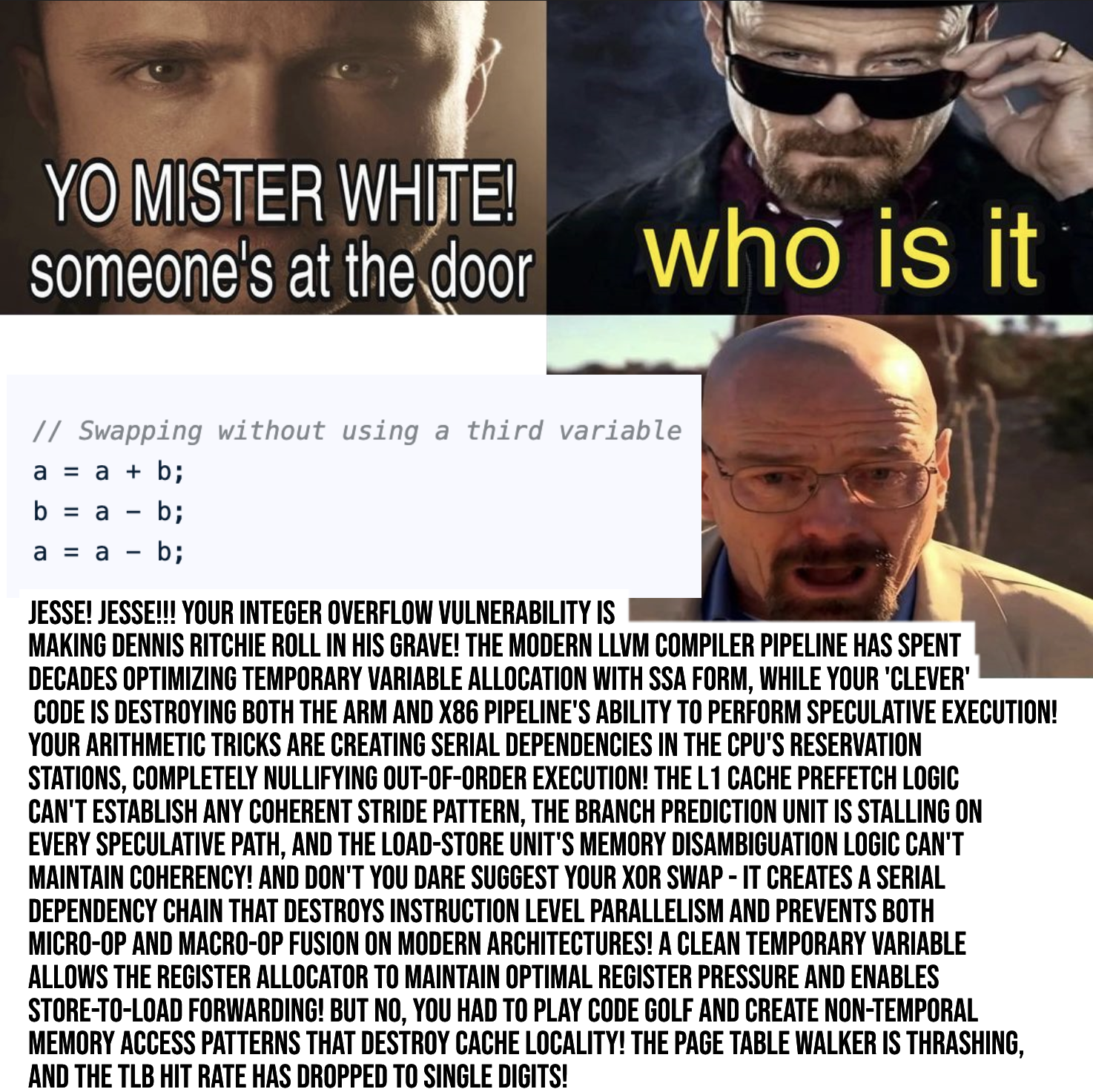

YO MISTER WHITE! someone's at the door who is it Swapping without using a third variable a a b: b a - b: a a - b; JESSE! JESSE!!! YOUR INTEGER OVERFLOW VULNERABILITY IS MAKING DENNIS RITCHIE ROLL IN HIS GRAVE! THE MODERN LLVM COMPILER PIPELINE HAS SPENT DECADES OPTIMIZING TEMPORARY VARIABLE ALLOCATION WITH SSA FORM, WHILE YOUR CLEVER CODE IS DESTROYING BOTH THE ARM AND X86 PIPELINE'S ABILITY TO PERFORM SPECULATIVE EXECUTION! YOUR ARITHMETIC TRICKS ARE CREATING SERIAL DEPENDENCIES IN THE CPU'S RESERVATION STATIONS, COMPLETELY NULLIFYING OUT-OF-ORDER EXECUTION! THE L1 CACHE PREFETCH LOGIC CAN'T ESTABLISH ANY COHERENT STRIDE PATTERN, THE BRANCH PREDICTION UNIT IS STALLING ON EVERY SPECULATIVE PATH, AND THE LOAD-STORE UNIT'S MEMORY DISAMBIGUATION LOGIC CAN'T MAINTAIN COHERENCY! AND DON'T YOU DARE SUGGEST YOUR XOR SWAP - IT CREATES A SERIAL DEPENDENCY CHAIN THAT DESTROYS INSTRUCTION LEVEL PARALLELISM AND PREVENTS BOTH MICRO-OP AND MACRO-OP FUSION ON MODERN ARCHITECTURESI A CLEAN TEMPORARY VARIABLE ALLOWS THE REGISTER ALLOCATOR TO MAINTAIN OPTIMAL REGISTER PRESSURE AND ENABLES STORE-TO-LOAD FORWARDING! BUT NO. YOU HAD TO PLAY CODE GOLF AND CREATE NON-TEMPORAL MEMORY ACCESS PATTERNS THAT DESTROY CACHE LOCALITY! THE PAGE TABLE WALKER IS THRASHING, AND THE TLB HIT RATE HAS DROPPED TO SINGLE DIGITS!

AI

AI

AWS

AWS

Agile

Agile

Algorithms

Algorithms

Android

Android

Apple

Apple

Bash

Bash

C++

C++

Csharp

Csharp